# ECS Transactions, 64 (6) 267-271 (2014) 10.1149/06406.0267ecst ©The Electrochemical Society

# **Ultra-Thin, High Quality HfO<sub>2</sub> on Strained-Ge MOS Capacitors with Low Leakage Current**

J. T. Teherani, W. Chern, D. A. Antoniadis, and J. L. Hoyt

Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139, USA

Ultra-thin HfO<sub>2</sub> MOS capacitors on strained-Ge (s-Ge) have been fabricated with an extracted effective oxide thickness (EOT) of 4.9 Å and leakage current less than 0.2 A/cm² at  $|V_G| < 0.5$  V. The CV measurements show little hysteresis and areal capacitance scaling for  $50\times50$  to  $200\times200~\mu\text{m}^2$  devices. A high series resistance is observed, likely due to a 500 meV valence band offset between the s-Ge and relaxed, p-type Si<sub>0.55</sub>Ge<sub>0.45</sub> virtual substrate. The capacitance results suggest an extremely-scaled, high quality dielectric on s-Ge promising for deeply scaled CMOS.

#### Introduction

Strained-Ge (s-Ge) is a promising channel material for future CMOS nodes due to its very high hole mobility (1,2) and compatibility with existing processes. Compressive strain further increases the high hole mobility of Ge (2–5). In comparison to Si, high quality dielectric interfaces for Ge are challenging due to the lack of an ideal native oxide. Much work has been performed developing high quality dielectrics for Ge, and recently published results show scaled dielectrics for unstrained Ge (6,7) and s-Ge (7,8). In this work, for the first time, we show an extremely-scaled (EOT < 5 Å), high quality dielectric on s-Ge. CV measurements of a MOS capacitor structure show areal capacitance scaling, little hysteresis, and low gate leakage current (< 0.2 A/cm<sup>2</sup> for  $|V_G|$  < 0.5 V).

#### **Fabrication**

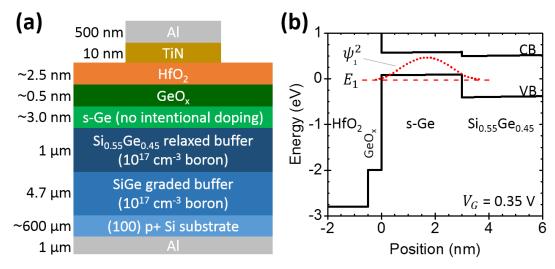

The epitaxial structure (shown in Fig. 1(a)) was grown by low-pressure CVD on a (100) p+ Si wafer. The epitaxial growth conditions were chosen to create a relaxed 1- $\mu$ m Si<sub>0.55</sub>Ge<sub>0.45</sub> virtual substrate (~10<sup>17</sup> boron doped) on which a nominally 6-nm-thick s-Ge layer with no intentional doping was grown. The s-Ge layer is compressively strained (2.2% biaxial) due to the lattice mismatch with the relaxed Si<sub>0.55</sub>Ge<sub>0.45</sub> virtual substrate. The s-Ge thickness is expected to be reduced to 3 nm after device processing.

The epitaxial wafer was cleaved into 3.2×3.2 cm pieces, and a 5-minute 1:10 (HCl:H<sub>2</sub>O) clean was completed before atomic layer deposition (ALD). The ALD process consisted of 1 minute of O<sub>3</sub> followed by 38 cycles (~3 nm) of HfO<sub>2</sub> deposition (with TEMAH and H<sub>2</sub>O as precursors), with both steps at 250 °C. This was followed by 400 cycles (~10 nm) of ALD TiN (with TiCl<sub>4</sub> precursor and N<sub>2</sub>/H<sub>2</sub> plasma) at 300 °C. After ALD, 500 nm of Al was sputtered on the front side of the wafer. A five-minute (~5 μm) BCl<sub>3</sub>/Cl<sub>2</sub> plasma etch was used to remove any epitaxial growth that may have occurred on the backside of the wafer, after which 1 μm of Al was sputtered on the backside of the piece. MOS capacitors were patterned using standard lithographic processes, and a final forming gas anneal (5% H<sub>2</sub>, 95% N<sub>2</sub>) was performed for 30 minutes at 450 °C. The final MOS capacitor structure (Fig. 1(a)) reflects the expected loss in the s-Ge due to the HCl clean and O<sub>3</sub> oxidation.

Figure 1. (a) Fabricated MOS capacitor structure with nominal thicknesses. (b) Energy band diagram of the simulated structure. Also shown are the first eigenenergy  $E_1$  and first hole wavefunction density  $\psi_1^2$  (shifted to align with  $E_1$ ) as a function of position.  $\epsilon_r$ =20 is used for both oxides in the simulation.

#### **Electrical Results**

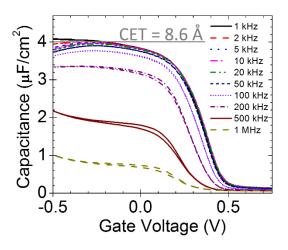

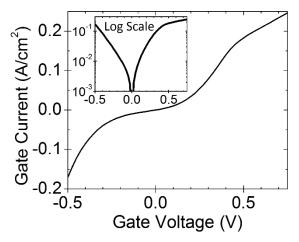

CV measurements of a  $100\times100~\mu m$  MOS capacitor show an uncorrected, as-measured CET of 8.6 Å (7.7 Å after series resistance correction) at V<sub>FB</sub> – 0.7V (Fig. 2). Large frequency dispersion exists for frequencies > 50 kHz due to a high series resistance likely caused by a 500 meV valence band offset (9) between s-Ge and Si<sub>0.55</sub>Ge<sub>0.45</sub> (Fig. 1(b)). The IV measurements (Fig. 3) show low gate leakage current ( $|J_G| = 0.17~\text{A/cm}^2$  at  $V_G = -0.5~\text{V}$ ), which translates to  $I_G = 17~\text{pA/}\mu m$  for  $L_G = 10~\text{nm}$ , well below the ITRS off-state requirements of ~100 A/cm² for high performance and low operating power devices (10).

Figure 2. Measured CV curves for a  $100\times100~\mu\text{m}^2~\text{s-Ge}$  MOS capacitor fabricated with 1 minute of O<sub>3</sub> and 38 cycles of HfO<sub>2</sub>. The plot shows little hysteresis and an 8.6-Å as-measured CET at  $V_G = -0.5~\text{V}$ .

Figure 3. Measured gate leakage for the s-Ge MOS capacitor shown in Fig. 2. The inset shows gate current on a log scale. Small gate leakage ( $|J_G| < 0.2 \text{ A/cm}^2$ ) is observed for  $|V_G| < 0.5 \text{ V}$ .

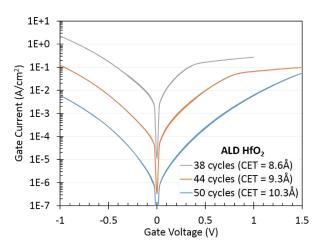

Two additional MOS capacitor samples were fabricated, and details are shown in Table 1. The gate leakage current for all three devices is shown in Fig. 4. A  $\sim$ 20× reduction in leakage current is seen by increasing the number of HfO<sub>2</sub> ALD cycles from 38 to 44 and from 44 to 50.

| Material                                         | Pre-ALD<br>clean             | ALD process                                                                  | CET (Å) | EOT (Å) |

|--------------------------------------------------|------------------------------|------------------------------------------------------------------------------|---------|---------|

| s-Ge on<br>Si <sub>0.55</sub> Ge <sub>0.45</sub> | 1:10<br>HCl:H <sub>2</sub> O | 1 min O <sub>3</sub><br>38 cycles HfO <sub>2</sub><br>400 cycles TiN         | 8.6     | 4.9     |

|                                                  | None                         | 1 min. O <sub>3</sub> 44 cycles HfO <sub>2</sub> 400 cycles TiN              | 9.3     | 5.7     |

|                                                  | None                         | 1 min. O <sub>3</sub><br><b>50</b> cycles HfO <sub>2</sub><br>400 cycles TiN | 10.3    | 6.8     |

Table 1. Details for the three fabricated s-Ge/GeO<sub>x</sub>/HfO<sub>2</sub> MOS capacitor wafers.

Figure 4. Measured gate current for different HfO<sub>2</sub> thicknesses.

# Simulation and Modeling

Quasistatic one-dimensional self-consistent coupled Poisson-Schrödinger electrostatic simulations were performed in order to extract EOT of the experimental devices. A strain-dependent  $6\times6$   $k\cdot p$  Hamiltonian (with deformation potentials from (9)) was used to calculate hole quantization in the s-Ge layer. In accordance with (11), a 2.1 eV valence band offset between Ge and GeO<sub>x</sub> was used in the simulations (Fig. 1(b)). The 500 meV valence band offset between s-Ge and Si<sub>0.55</sub>Ge<sub>0.45</sub> creates a deep quantum well confining most of the holes in the s-Ge layer (9).

The simulated CV curves were quite insensitive to s-Ge thickness and SiGe doping level. Decreasing the s-Ge thickness from 5 to 3 nm resulted in a marginally steeper rise in the simulated capacitance when transitioning from hole depletion to accumulation, but the extracted EOT was not significantly affected. The simulations shown in this paper use 3-nm s-Ge thickness and  $10^{17}$  p-type doping in the SiGe layer, consistent with experimentally expected values.

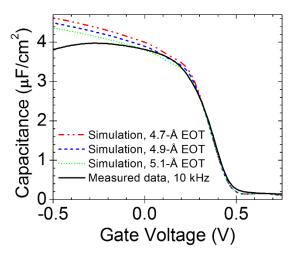

Fig. 5 shows the 10 kHz experimental CV (for 38 cycles of HfO<sub>2</sub>) with simulated quasistatic CV curves for structures with varying EOT. The mismatch of the simulated and experimental curves in strong hole accumulation is due to both a large series resistance ( $R_s \sim 0.1 \ \Omega \cdot \text{cm}^2$ ) and large gate conductance ( $G_t \sim 0.4 \ \text{S/cm}^2$  at  $V_G = -0.5 \ \text{V}$ ), which causes a sizable error when transforming the measured impedance to a two-element parallel capacitance  $C_P$ , parallel conductance  $G_P$  circuit model (12).

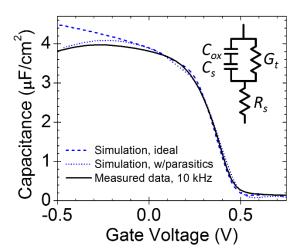

A circuit model incorporating parasitic gate tunneling conductance  $G_t$  and series resistance  $R_s$  (inset of Fig. 6) is applied to an ideal simulated CV in order to recover the measured CV result yielding an extracted EOT of 4.9 Å (Fig. 6). This is the smallest known EOT for a high quality dielectric on s-Ge published to date. Other recent results include 7-Å, 9-Å, and 10-Å EOT on s-Ge (7,8,13), and an 8-Å CET on unstrained Ge (6).

Figure 5. Simulated quasistatic CVs for the structure shown in Fig. 1(b) with varying EOT and measured CV for a MOS capacitor with 38 cycles of HfO<sub>2</sub> (multifrequency CV shown in Fig. 2). A large series resistance in addition to gate leakage causes deviation between measurement and simulation in strong hole accumulation.

Figure 6. Simulated CV for a 4.9-Å EOT. The inset shows the circuit model used to correct for parasitics. Parasitic tunneling conductance  $G_t$  and series resistance  $R_s$  are applied to the ideal simulation to recover the measured CV.  $R_s$  and  $G_t$  were extracted by comparing DC and HF (200 kHz) measured conductance.

# **Benchmarking**

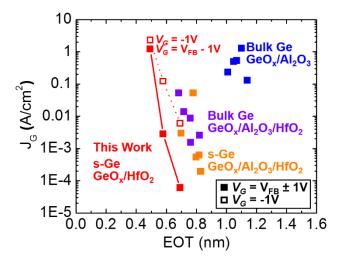

Fig. 7 compares the gate current as a function of EOT for MOS capacitors fabricated in this work and by Zhang (7,14). Thinner EOT is achieved by replacing Al<sub>2</sub>O<sub>3</sub> with HfO<sub>2</sub>, due to HfO<sub>2</sub>'s larger relative permittivity. The figure shows an exponential increase in gate current with decreasing EOT. Gate leakage current obtained in this work is comparable with previous results on bulk and s-Ge.

Figure 7. Gate current as a function of EOT for capacitors in this work (red symbols) and Zhang's (7,14). In keeping with previous publications, the gate current is given at  $V_{FB} + 1V$  for n-type and  $V_{FB} - 1V$  for p-type material (both shown with closed symbols) in order to compare devices at similar carrier densities. However, the comparison is imperfect because

$V_{FB}$  varies due to different 1) work function metals, 2) substrate doping, and 3) dielectric charges, such that the absolute gate voltage can vary significantly for different data points. The devices in this work are also compared at a fixed  $V_G = -1$ V (open symbols) to account for  $V_{FB}$  differences, which brings this work's results in line with previous data.

### **Summary**

In summary, s-Ge/GeO<sub>x</sub>/HfO<sub>2</sub> MOS capacitors (with O<sub>3</sub> surface passivation) demonstrated a 4.9-Å EOT and low gate leakage  $< 0.2 \text{ A/cm}^2$  at  $|V_G| < 0.5 \text{ V}$ . The capacitors show little hysteresis, but significant frequency dispersion due to a high resistance caused by a large 500 meV valence band offset between s-Ge and the Si<sub>0.55</sub>Ge<sub>0.45</sub> substrate. An exponential decrease in gate leakage current is shown for increasing HfO<sub>2</sub> ALD cycles. The results show a promising ultra-scaled, high quality dielectric on s-Ge with low leakage current.

## Acknowledgments

This work was completed at the Microsystems Technology Laboratories at MIT and supported by an NSF Graduate Fellowship and the NSF Center for Energy Efficient Electronics Science (award EECS-0939514).

#### References

- 1. W. Chern, P. Hashemi, J. T. Teherani, D. A. Antoniadis, and J. L. Hoyt, *IEEE Electron Device Lett.*, **35**, 309–311 (2014).

- 2. S. Thompson, G. Sun, K. Wu, J. Lim, and T. Nishida, *IEEE International Electron Devices Meeting (IEDM)*, p. 221–224 (2004).

- 3. H. Irie, K. Kita, K. Kyuno, and A. Toriumi, *IEEE International Electron Devices Meeting (IEDM)*, p. 225–228 (2004).

- 4. L. Gomez, C. Ni Chléirigh, P. Hashemi, and J. L. Hoyt, *IEEE Electron Device Lett.*, **31**, 782–784 (2010).

- 5. J. T. Teherani, W. Chern, D. A. Antoniadis, and J. L. Hoyt, *IEEE International Electron Devices Meeting (IEDM)*, p. 32.4.1–32.4.4 (2013).

- 6. B. Duriez et al., *IEEE International Electron Devices Meeting (IEDM)*, p. 20.1.1–20.1.4 (2013).

- 7. R. Zhang et al., *IEEE International Electron Devices Meeting (IEDM)*, p. 26.1.1–26.1.4 (2013).

- 8. P. Hashemi et al., *IEEE Electron Device Lett.*, **33**, 943 –945 (2012).

- 9. J. T. Teherani et al., *Phys. Rev. B*, **85**, 205308 (2012).

- 10. ITRS Front End Process (FEP) Tables (2012).

- 11. V. V. Afanas'ev et al., Appl. Phys. Lett., **92**, 022109 (2008).

- 12. E. M. Vogel, W. K. Henson, C. A. Richter, and J. S. Suehle, *IEEE Trans. Electron Devices*, 47, 601–608 (2000).

- 13. W. Chern et al., *IEEE International Electron Devices Meeting (IEDM)*, p. 16.5.1–16.5.4 (2012).

- 14. R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, *IEEE Trans. Electron Devices*, **59**, 335–341 (2012).